Modern integrated circuits (ICs) have required continuous scaling of field-effect transistors (FETs) to afford higher density, superior performance, and better energy efficiency. However, the scaling of Si-based transistors requires continuous reduction of the transistor body thickness in order to suppress short channel effects. Doing so would cause a large reduction in carrier mobility due to stronger phonon and surface scattering effects in 3D crystalline semiconductors as the fin width or GAA body thickness is reduced to < 4 nm [1-3]. To tackle these notorious short-channel effects in aggressively scaled FETs, ultrathin semiconducting channels possessing high carrier mobility, such as 2D [4-6] and 1D [7-10] materials such as TMD (Transition-Metal-Dichalcogenides like MoS2 and WSe2…), graphene ribbon and CNT (carbon nanotubes), are attractive.

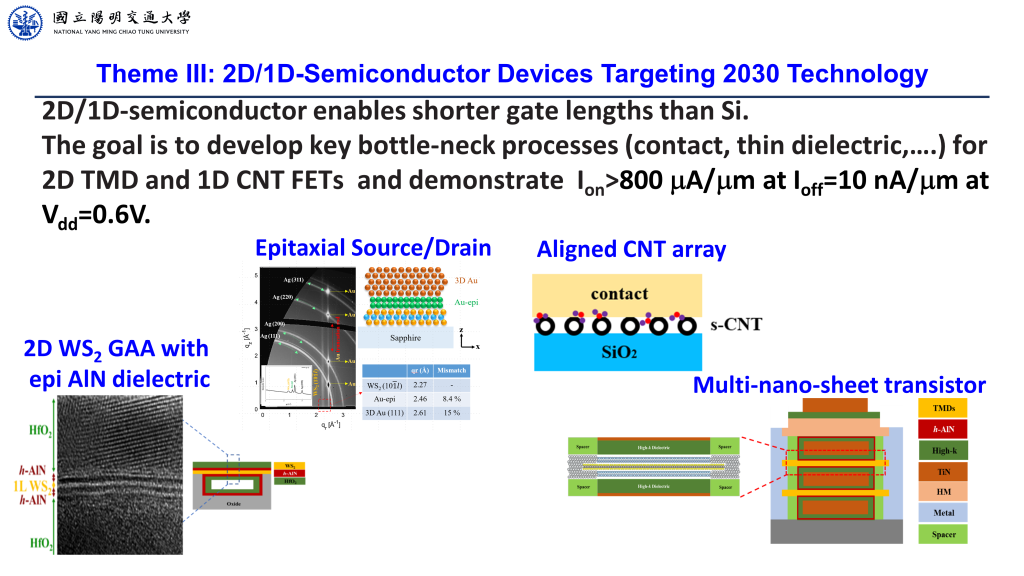

In spite of the theoretical benefits, researchers are still struggling to make these candidates perform as well as conventional Si-based transistors. Challenges include low contact resistance, high-quality and thin uniform gate dielectrics, steep subthreshold swing, and large on-current at low operating voltage. In this proposal, we focus on developing devices targeting 2030 technology. We plan to study and demonstrate proposed solutions with small top-gated devices with 2D and 1D channels using several novel techniques to meet stringent performance requirements and to provide a guide to future industry. The goal of this project is to identify and develop new technologies to support the industrial production of TMD and CNT FETs with Ion > 800 mA/mm at Ioff = 10 nA/mm and Vdd = 0.6 V.

[1] C. Auth et al., IEEE International Electron Devices Meeting (IEDM), pp. 29.1.1-29.1.4, Dec. 2017 [2] G. Bae et al., IEEE International Electron Devices Meeting (IEDM), pp. 28.7.1-28.7.4, Dec. 2018 [3] S. Liu et al., The Royal Society of Chemistry, Nanoscale, vol. 13, pp. 5536–5544, Feb. 2021, doi: 10.1039/D0NR09094H [4] X. Xiong, A. Tong, X. Wang, S. Liu, X. Li, R. Huang, and Y. Wu, 2021 IEEE International Electron Devices Meeting (IEDM), Dec. 2021, pp. 7.5.1-7.5.4, doi: 10.1109/IEDM19574.2021.9720533.[5] X. Huang, C. Liu, Z. Tang, S. Zeng, L. Liu, X. Hou, H. Chen, J. Li, Y. G. Jiang, D. W. Zhang, and P. Zhou, IEEE International Electron Devices Meeting (IEDM), Dec. 2020, pp. 12.1.1-12.1.4, doi: 10.1109/IEDM13553.2020.9371941. [6] R. Zhou and J. Appenzeller, 2018 76th Device Research Conference (DRC), Jun. 2018, pp. 1-2 [7]Franklin et al, Science 378, 726-732, 2022 [8] Chau, R. et al. Benchmarking nanotechnology for high-performance and low-power logic transistor [9] George, S. et al. ACS Nano 8, 8730–8745 (2014).[10] 20 years of nanotube transistors. Nat. Electron. 1, 149 (2018).